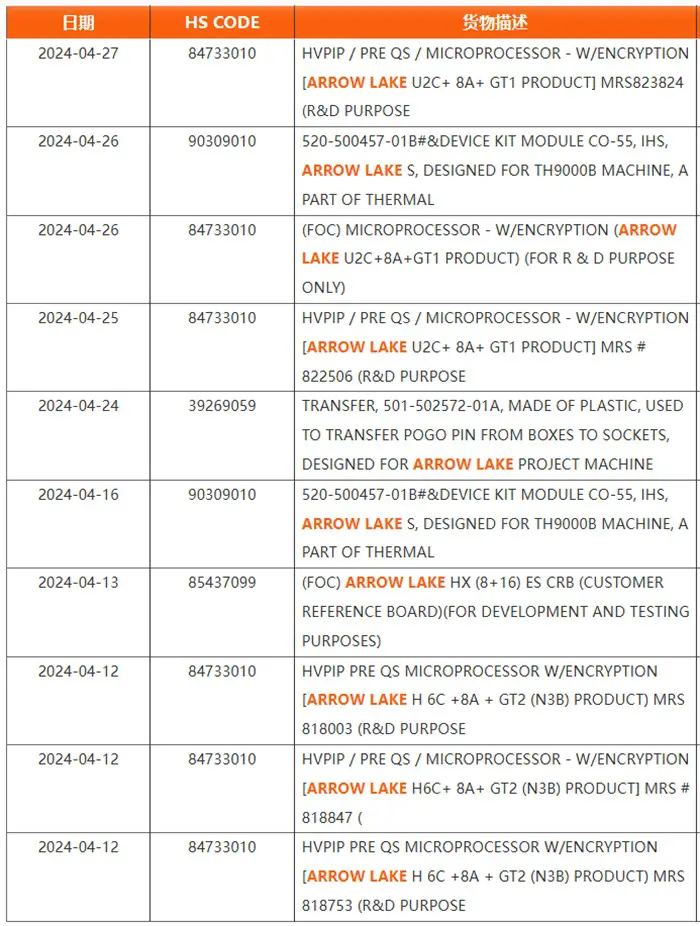

Recently, several Intel Arrow Lake and Panther Lake chips designed for mobile platforms have appeared on shipping lists. The former belongs to the Core Ultra 200 series arriving in early 2025, while the latter is part of the Core Ultra 300 series set for 2026. Information noted on customs shipping lists may reveal the process technology used for these chips.

According to Wccftech, Arrow Lake will span multiple sub-platforms, covering desktop and laptop products. “S” will denote desktop, “HX” will be for enthusiast-grade gaming laptops, “H” for high-performance laptops, and “U” for low-power mobile devices. The shipping lists feature three Arrow Lake chips: Arrow Lake-U, Arrow Lake-H, and Arrow Lake-HX. The integrated graphics of Arrow Lake-U is labeled GT1, while Arrow Lake-H features GT2.

The Arrow Lake-H details on the shipping list indicate the use of the N3B process, although specific modules were not mentioned. Rumors suggest that Intel plans to use the N3B process for the compute modules and the N4 process for the GPU modules. It is still uncertain if any Arrow Lake chips, like Lunar Lake, will be entirely manufactured by TSMC.

Known Arrow Lake chips include:

- Arrow Lake-S 24-Core 8+16 (LGA 1851) – 3.6 GHz / 36 MB L3 Cache

- Arrow Lake-S 14-Core 6+8 (LGA 1851) – 2.8 GHz / 24 MB L3 Cache

- Arrow Lake-S 6-Core 6+0 (LGA 1851) – 2.8 GHz / 18 MB L3 Cache

- Arrow Lake-HX 16-Core 8+8 (FCBGA) – 2.9 GHz / 30 MB L3 Cache

- Arrow Lake-HX 14-Core 6+8 (FCBGA) – 3.0 GHz / 24 MB L3 Cache

- Arrow Lake-H 14-Core 6+8 (FCBGA) – TBD

- Arrow Lake-U 10-Core 2+8 (FCBGA) – TBD

Additionally, there are several Panther Lake chips, including Panther Lake-UH, Panther Lake-UPH, and Panther Lake-P. These chips are currently being evaluated on reference platforms. Recently, Intel announced that they have successfully powered Panther Lake components using the Intel 18A process.

Unlike Arrow Lake, Panther Lake will also cover the product line of Lunar Lake, with replacement products likely to integrate memory packaging.