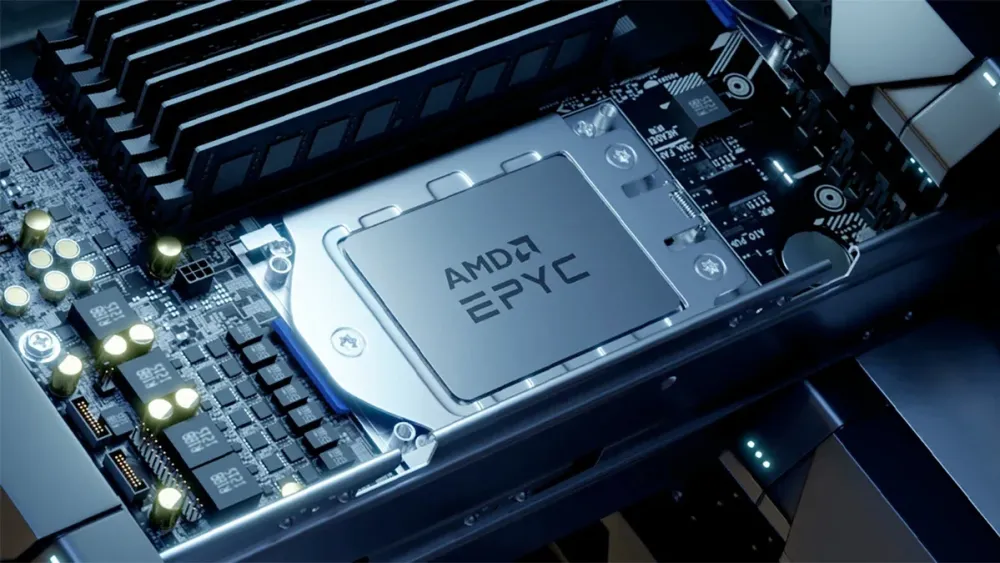

Last year, AMD announced its transition to the Zen 6 architecture, designed to span both 3nm and 2nm process nodes, with plans to implement it in the sixth-generation EPYC server processors—codenamed Venice—as well as in upcoming consumer-grade Ryzen series processors. AMD has now officially confirmed its collaboration with TSMC to integrate the advanced N2 (2nm) process technology into the Venice EPYC line and has already completed the tape-out phase for the chip.

The sixth-generation Venice EPYC processors are expected to launch on schedule in 2026. Concurrently, AMD has also announced that its Zen 5-based fifth-generation EPYC processors, codenamed Turin, have successfully gone online at TSMC’s new fabrication plant in Arizona and passed the required validation procedures.

Dr. Lisa Su, AMD Chair and CEO, remarked, “TSMC has been an essential partner to AMD for many years. Our deep collaboration with their R&D and manufacturing teams enables us to consistently deliver industry-leading products that redefine the boundaries of high-performance computing. Becoming the first HPC customer to leverage TSMC’s N2 process and the Arizona Fab 21 underscores how closely we work together to advance innovation and bring next-generation technologies to life.”

Dr. C.C. Wei, TSMC Chairman and CEO, added, “We are honored to have AMD as the first HPC customer utilizing our cutting-edge 2nm (N2) process technology and manufacturing at our Arizona facility. Through our partnership, we are driving significant technological advancements that deliver superior performance, power efficiency, and yield for high-performance chips. We look forward to continued close collaboration with AMD as we usher in a new era of computing.”