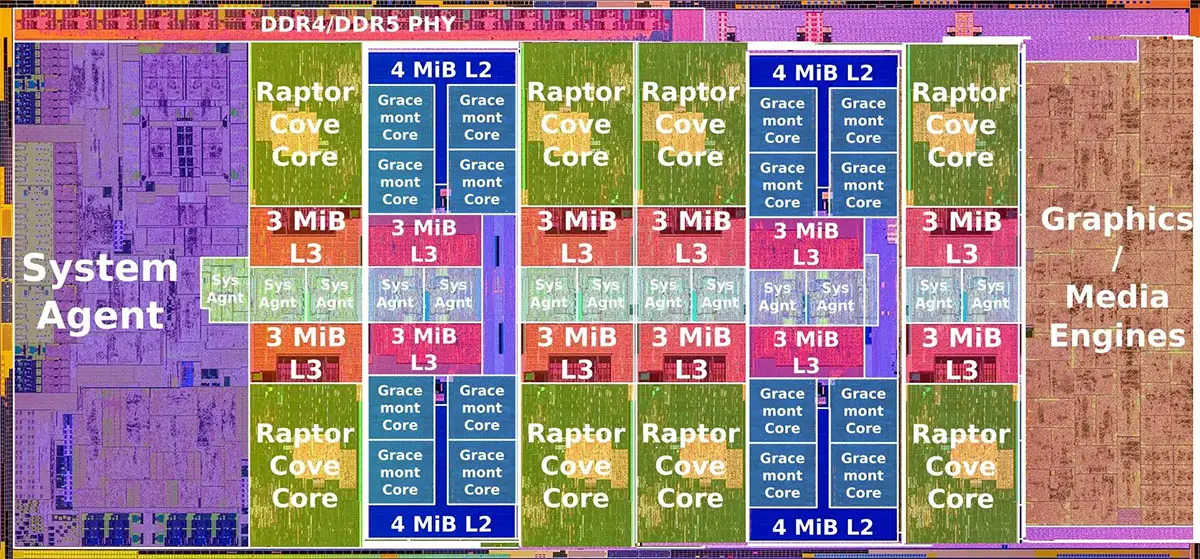

Intel plans to release the next-generation Arrow Lake processors in 2024, with P-Cores and E-Cores upgraded to the new Lion Cove and Skymont architectures, respectively. Arrow Lake will extend across multiple sub-platforms, with the “S” series designated for desktops, belonging to the Core Ultra 200 series, utilizing the new LGA 1851 socket, replacing the existing LGA 1700 socket.

Recently, it was revealed that Arrow Lake-S will feature two types of chips: the 8P+16E “B0” and the 6P+8E “C0,” with integrated graphics comprising up to four Xe cores.

The B0 chip will primarily be used in the Core Ultra 9 and Core Ultra 7, with the former supporting up to 8P+16E configurations and the latter up to 8P+12E. Both will be available in 125W “K,” 65W “non-K,” and 35W “T” versions, with four Xe cores for the integrated graphics, and potentially “F” models without integrated graphics. The Core Ultra 5 will feature a mix of B0 and C0 chips, supporting configurations up to 6P+8E (4Xe), as well as 6P+8E (3Xe), 6P+8E (0Xe), and 6P+4E (2Xe) combinations. Notably, the 35W “T” version will not include the 6P+8E (0Xe) configuration, and low-power products will exclusively use C0 chips.

In addition to the Ultra 9 285K (8P+16E, 125W), Ultra 9 275 (8P+16E, 65W), Ultra 7 265K (8P+12E, 125W), Ultra 7 255 (8P+12E, 65W), and Ultra 5 245K (6P+8E, 125W), the specific naming of other models has yet to be determined.

Rumors suggest that in Arrow Lake-S, each Skymont-architecture E-Core cluster (comprising four cores) will be equipped with 4MB (16-Way) of L2 cache and 3MB of L3 cache, while each Lion Cove-architecture P-Core will feature 3MB (12-Way) of L2 cache and 3MB of L3 cache. This means that the highest 8P+16E configuration will include 40MB of L2 cache and 36MB of L3 cache, totaling 76MB, which is approximately 12% more cache than the 68MB found in Raptor Lake-S.