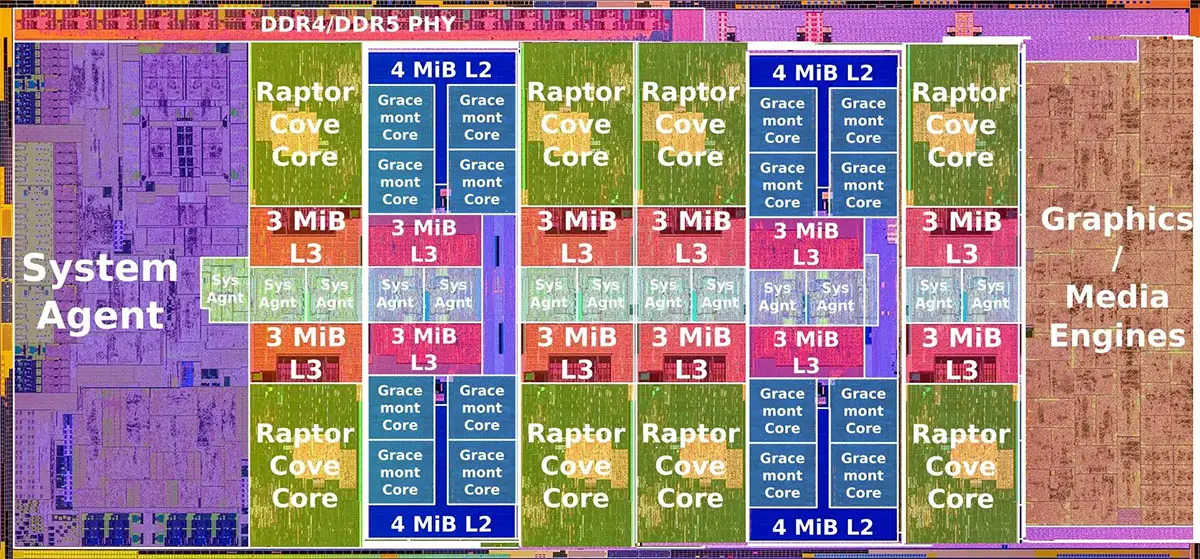

Currently, Intel‘s 12th to 14th generation Core and Core Ultra 100 processors, including Alder Lake, Raptor Lake, and Meteor Lake, feature P-Cores and E-Cores connected to a ring bus, sharing an L3 cache. The layout is similar, with P-Cores concentrated on one side and E-Cores on the other. For single-chip processors like Alder Lake and Raptor Lake, the bidirectional ring bus communicates in the following sequence: one half of the P-Cores, one half of the E-Core cluster, iGPU, the other half of the E-Core cluster, the other half of the P-Cores, and Uncore. In the chiplet-designed Meteor Lake, the computation module contains only CPU cores, simplifying the ring bus structure.

However, according to @Kepler_L2, Intel will change this configuration in the next-generation Arrow Lake. The P-Cores and E-Cores will be arranged in an interleaved manner. The accompanying diagram provides an approximate representation of this new layout, which is structurally similar to Meteor Lake, with the computation module lacking a memory controller, integrated graphics, and Uncore.

Why is Arrow Lake adopting this new configuration? First, interleaving P-Cores and E-Cores helps reduce communication latency between them. The new hardware thread scheduler prioritizes assigning tasks to E-Cores, only moving them to P-Cores when higher performance is required, making the reduction of E-Core to P-Core communication latency crucial.

Additionally, this arrangement helps disperse heat sources. Users running stress tests on the 12th and 14th-generation Core processors know that P-Cores run significantly hotter than E-Cores. Separating the P-Cores distributes the heat sources, aiding in heat dissipation.