GPUsAreMagic

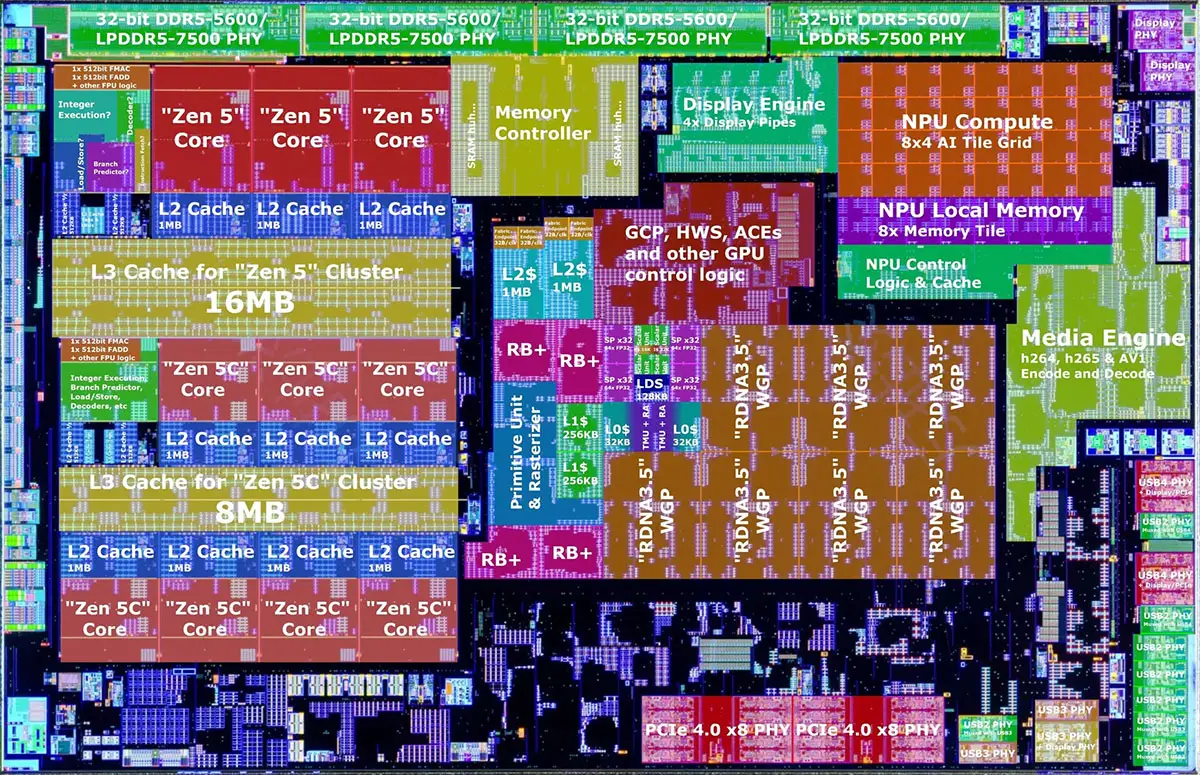

Laptops equipped with AMD Ryzen AI 300 series processors went on sale a couple of days ago, and information about the new Strix Point processor is beginning to emerge. This processor employs the more advanced TSMC N4P process, but its core size is significantly larger than the previous generation, measuring 12.06 x 18.71 mm compared to Phoenix and Hawk Point’s 9.06 x 15.01 mm. The increased size is natural to accommodate a larger CPU, GPU, and NPU.

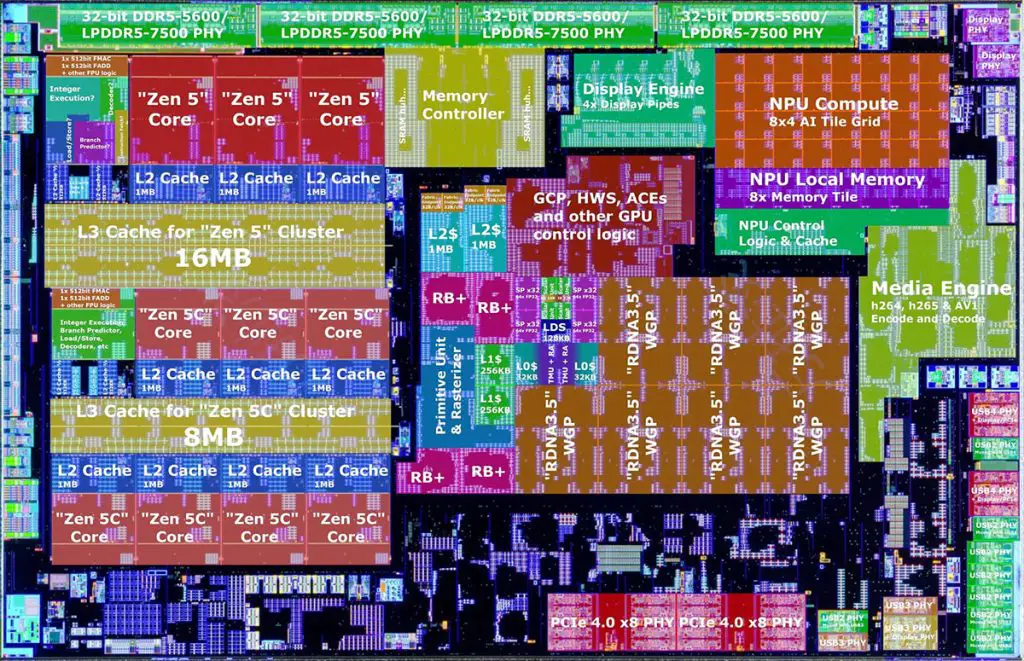

Strix Point features 12 CPU cores distributed across two CCX units. One CCX contains 4 Zen 5 cores with 16MB of L3 cache, while the other houses 8 Zen 5c cores with 8MB of L3 cache. It appears that Zen 5c cores are not much smaller than Zen 5 cores. The two CCX units are connected to the rest of the CPU components via the IF bus.

A massive integrated GPU sits at the center of the CPU chip, based on the RDNA 3.5 architecture. It includes 8 WGPs, 16 CUs, 1024 stream processors, 4 render backends (equivalent to 16 ROPs), numerous logic control circuits, and 2MB of L2 cache. The media and display engines are located to the right and above the GPU, respectively, supporting a variety of video formats including H.264, H.265, and AV1. The display engine encodes the GPU’s frame output into various video interface formats, supporting up to 4 video outputs, with the physical layer for video output situated at the edge of the CPU.

The NPU in Strix Point is considerably larger than its predecessor, utilizing the next-generation XDNA 2 architecture and featuring 32 AI engines. Additionally, the NPU has its cache. According to AMD, the new NPU’s computational power reaches 50 TOPS, surpassing Microsoft’s hardware requirements for Copilot+.

Four 32-bit memory controllers are located on one edge of the CPU, supporting DDR5-5600 and LPDDR5-7500 memory. These controllers have SRAM cache, although the specific capacity is not disclosed. This caching design is also present in the Phoenix and Phoenix 2 chips, but not in the IOD of desktop processors.

In the last three generations of mobile processors, AMD has been reducing the number of PCIe lanes. Cezanne had 24 PCIe lanes, Phoenix reduced it to 20, and Strix Point further reduced it to 16 lanes, with 4 lanes allocated to USB4, leaving only 12 lanes available for other uses.