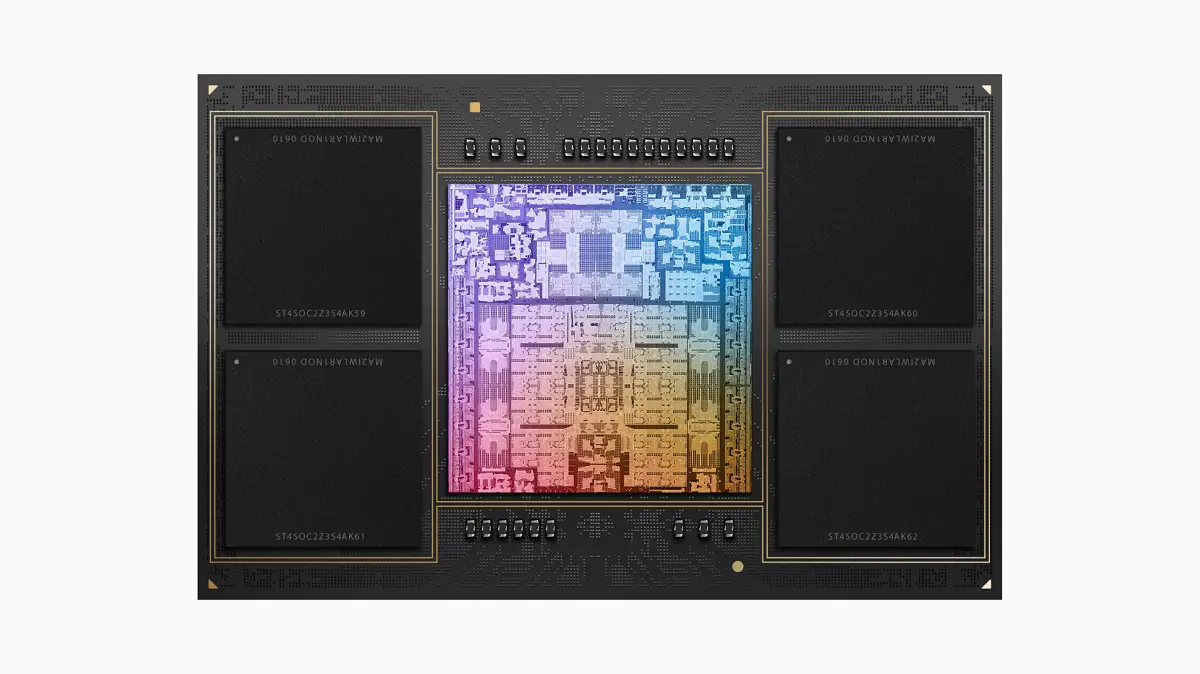

It was previously reported that Apple is exploring the use of TSMC’s SoIC technology, having already conducted small-scale testing in preparation for future chip designs. As TSMC’s largest customer, contributing to approximately a quarter of its revenue, Apple has consistently invested in advanced process nodes, fostering a close collaboration in cutting-edge chip manufacturing over recent years.

According to TrendForce, Apple has joined AMD in becoming a customer of SoIC packaging, with plans to implement the new technology by 2025. TSMC’s 3D Fabric system integration platform categorizes advanced packaging into three parts: SoIC for front-end 3D chip stacking technology, and CoWoS and InFo series for back-end advanced packaging.

In recent times, there have been frequent reports of capacity shortages for CoWoS packaging, prompting TSMC to continuously enhance its production capabilities. However, SoIC packaging is different, facing fewer bottlenecks. Since beginning small-scale production of SoIC packaging in 2022, TSMC’s long-term plan is to expand SoIC packaging capacity by more than twentyfold by 2026 to meet the growing demand. With Apple’s involvement, TSMC is expected to accelerate this capacity expansion.

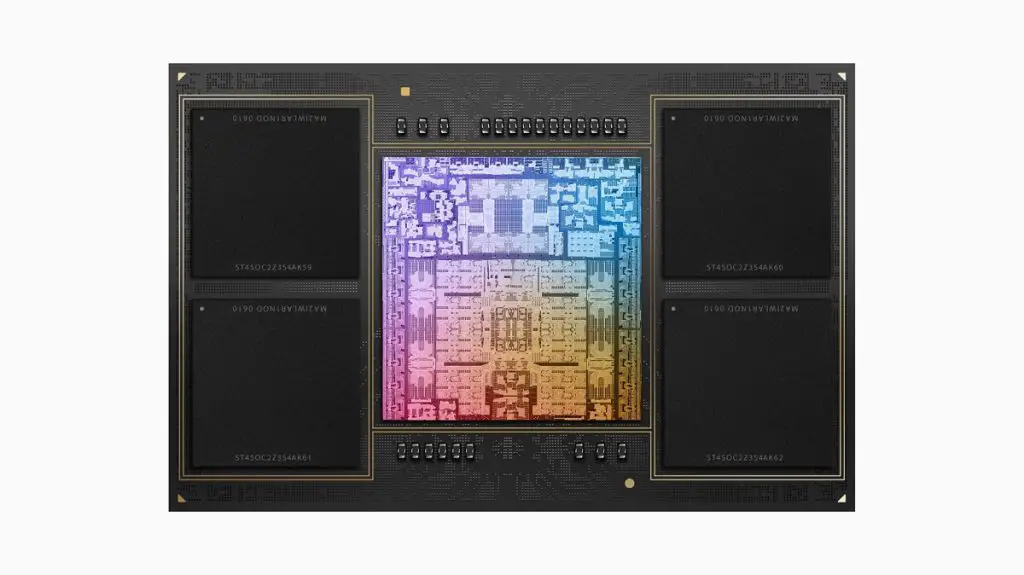

Over the past two years, AMD’s success with the Ryzen 5000/7000X3D series can be attributed to the support of TSMC’s 3DFabric advanced packaging platform. Their 3D V-Cache technology, rooted in the Hybrid Bond concept of advanced packaging, has significantly benefited from TSMC’s SoIC+CoWoS services in high-end chips. In recent years, AMD has adopted a bold and progressive approach to technology selection, successfully integrating advanced packaging technology across its product lines, a move observed by other manufacturers.

In last year’s release of the Instinct MI300 series, AMD not only utilized TSMC’s 5nm process but also incorporated various packaging technologies, including SoIC-X to stack CPU and GPU chips on a base chip, further integrating them into CoWoS packaging.

SoIC, as a packaging method based on CoWoS+WoW, offers several advantages over traditional 2.5D solutions. It not only reduces overall power consumption but also provides higher density and faster transfer rates, resulting in greater memory bandwidth. Another benefit of SoIC is its small footprint, allowing Apple the flexibility to mass-produce smaller chips and save space. Additionally, SoIC technology reduces the cost of integrated circuit boards, leading to significant cost savings.